��ȱ��EUV��̙C(j��)����r�£�����(n��i)�댧(d��o)�w�ИI(y��)��Ҫ��هDUV���F(xi��n)�����M(j��n)�Ĺ�ˇ�����g(sh��)����(zh��n)�O���_�e늡�Intelֻ�õ���7nm��(ji��)�c������(n��i)�tҪ����(zh��n)3nm�����¹�ˇ��

DUV���a(ch��n)3nm��ˇ���R��һ��ƿ�i���}���Ǿ��ȿ��ƣ��Ͼ������ع����ǰ�l(f��)���ᵽ����(n��i)ij�C(j��)��(g��u)��DUV��W(xu��)ϵ�y(t��ng)�����r���������@������(zh��n)������ϵ�y(t��ng)�����Բ��㌧(d��o)�¾��A�ع⾀��һ����ƫ��^��2nm���o���M��3nm��(ji��)�c�Ĺ�ˇҪ��

ԓ��˾��B�������Ľ�Q���������W(xu��)�Ĥ�F(tu��n)��O(sh��)Ӌ�˶��ӽ��|(zh��)ӲĤ������

Ĥ�ӽY(ji��)��(g��u)������SiO₂��Ta₂O₅������e�����Ӕ�(sh��)40-60�ӣ�

��ˇ����(sh��)���x���o�����e��IAD�����g(sh��)�����לض�250�棬������(qi��ng)2��10⁻⁵Pa��

�P(gu��n)�Iָ��(bi��o)�����IJ��L193��0.2nm����ֵ�^�ʣ�92%����ֹ���OD6�������^�ʣ�10⁻⁶����

��K�Y(ji��)������أ����������Ĕ�(sh��)��(j��)���£�

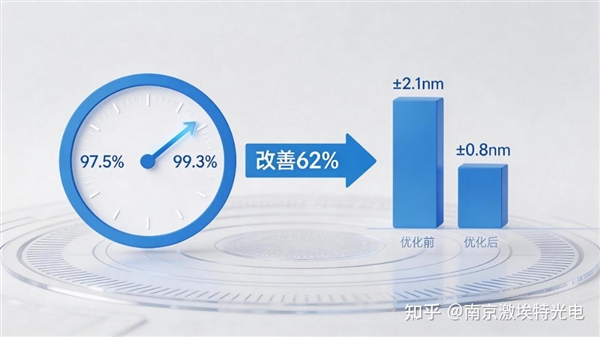

�ع��|(zh��)�����������AƬ��(n��i)���������ԏġ�2.1nm��������0.8nm�������A(y��)������5-8%��

����(zh��n)������ߣ�����(zh��n)ϵ�y(t��ng)��λ���ȏġ�1.5nm��������0.8nm��

ϵ�y(t��ng)��(w��n)��������(qi��ng)���B�m(x��)����100С�r��·Ư�����p��70%��

�@һ����Ҳ�õ��˿͑�F(tu��n)꠵��J(r��n)�ɣ���ʾ�����صļ��g(sh��)�������H��Q�����������Ԇ��}����V��Ƭ�Ď���������������ϵ�y(t��ng)���w�����������3�����e���R��е����ξ��ȿ��ƣ��_(d��)�����҂�֮ǰδ�܌��F(xi��n)�Ħ�/10ˮƽ������m(x��)��ˇ�����A(y��)���˳���ļ��g(sh��)������

�����@һ���g(sh��)��ο����أ������ع�늵Ĺ�W(xu��)�Ĥ���g(sh��)��DUV��W(xu��)ϵ�y(t��ng)�ľ��������ԏ�2.1nm������0.8nm��ͬ�r����(zh��n)ϵ�y(t��ng)����Ҳ��1.5nm��������0.8nm���@��DUV���a(ch��n)���M(j��n)�Ƴ�оƬ�o�ɺ���Ҫ����龫�Ȳ��У����a(ch��n)��оƬ�ǏU�ģ�������DUV��������5nm��3nmоƬ���ǘO�y�ġ�

���^�@��ľ���߀���ǹ�̙C(j��)��Overlay�̾��ȣ�������̾���0.8nm���DZ�EUV��̙C(j��)��Ҫţ�ˣ����@���M(j��n)չҲֵ�Ñc�R����ζ������(n��i)�ďS������DUV�㶨3nm��ˇоƬ�ѽ�(j��ng)����һ���̶ȣ�����߀�]���a(ch��n)������ͨ����߀���Б�ġ�

�@�����g(sh��)����ȫ�����Ҳ�Ǫ�һ�o���ģ�����_�e늡����Ǽ�Intel��5nm����7nm��(ji��)�c��ȫ�憢��EUV����ˣ�����Ҳ�]���@�ӵ��аl(f��)��(j��ng)

|