�S�����g�İlչ�͌����ܿ��]��ģ�M�·�������Ƶ�һ���·�ăɶˣ�����̖��Ќ����F����Ĕ��ֽӿڡ��@�Ӽ��ܱ���ģ�M�·���߾������ܵ�Ӱ����ܹ�ʡ�·���D2�o����һ�������������l�ӿڵ����ӡ�

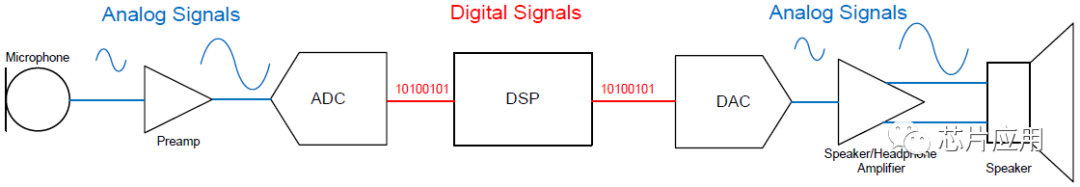

�D1. ���y�����l��̖�·

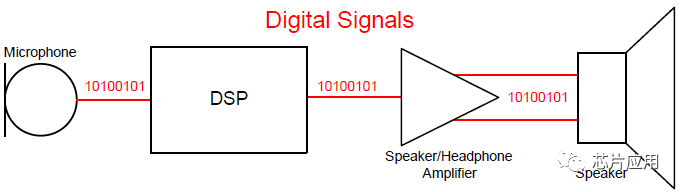

�D2. �������l��̖�·

�������l��̖�ij�Ҋ��ݔ�˜ʣ���I2S��PCM (Pulse Code Modulation) ��PDM (Pulse DensityModulation)����Ҫ����ͬһ�K�·����оƬ֮�g���l��̖�Ă�ݔ��Intel HDA (Intel High DefinitionAudio) ����PC��Audio��ϵ�y���������ã� S/PDIF��Ethernet AVB��Ҫ�����ڰ��g�L���x����Ҫ��|�B�ӵĈ��ϡ�

�@����Ҫ�Ƚ�BI2S�������l�ӿڡ�

I2Sȫ�QInter-IC Sound, Integrated Interchip Sound����I2S�����w������1986�궨�x�Ĕ������l��ݔ�˜ʣ����ڔ������l������ݔ�����˶������w���ֶ��x�⣬I2S��I2C�]���κ��Pϵ��

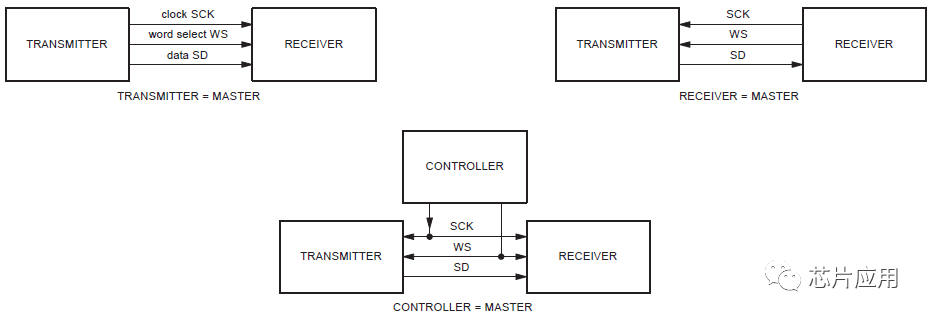

I2S�DZ��^���εĔ��ֽӿڅf�h���]�е�ַ���O���x��C�ơ���I2S�����ϣ�ֻ��ͬ�r����һ�����O��Ͱl���O�������O������ǰl���O�䣬Ҳ�����ǽ����O�䣬���Džf�{�l���O��ͽ����O������������O�䡣��I2Sϵ�y�У��ṩ�r犣�SCK��WS�����O������O�䡣�D3�dz�Ҋ��I2Sϵ�y��D��

�D3 I2Sϵ�yͨ�����ÿ�D

I2S�����ɂ�����Left/Right���Ĕ����������O��l�����x��/���x��WS���������M�������������ГQ��ͨ�^����I2S�ӿڵĔ�Ŀ������I2S�O����Ԍ��F������Multi-Channels�����á�

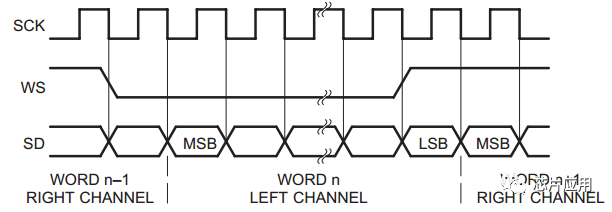

��I2S��ݔ�f�h�У�������̖���r���̖�Լ�������̖�Ƿ��_��ݔ�ġ�I2S�f�hֻ���x������̖�����r���̖SCK��������̖SD���������x����̖WS��

SCK��ģ�K�ȵ�ͬ����̖����ģʽ�r���ⲿ�ṩ����ģʽ�r��ģ�K�Ȳ��Լ��a������ͬ�S�ҵ�оƬ��̖���r���̖�з����ܲ�ͬ��Ҳ���ܷQBCLK/Bit Clock��SCL/Serial Clock

SD�Ǵ��Д�������I2S�������M���a�a����ʽ�ڔ������ς�ݔ����WS׃����ĵ�һ��SCK�}�_���Ȃ�ݔ���λ��MSB, Most Significant Bit�����Ȃ���MSB�����l���O��ͽ����O������L���ܲ�ͬ����ϵ�y���L�Ȕ����l�Ͷ����L�L�ĕr������ݔ�͕����F�ؔ�ĬF��/Truncated��������������ն˽��յĔ���λ����Ҏ�������L�L��Ԓ����ôҎ�����L���λ��LSB: Least Significant Bit���Ժ������λ���������ԡ�������յ����L����Ҏ�������L�̣���ô���������λ������0���a��ͨ�^�@�N��ʽ����ʹ���l��̖�������Чλ�õ���ݔ���Ķ����C��õ� �XЧ����

�� ����ݔ���ݔ�����ԣ���ͬоƬ�ϵ�SDҲ���ܷQSDATA��SDIN��SDOUT��DACDAT��ADCDAT�ȣ�

�� �����l�ͼȿ���ͬ����SCK�������أ�Ҳ�������½��أ��������O����SCK�������زɘӣ��l�͔����r���迼�]

WS�����x����̖�����������l�Ͷ����x�����������

�� WS��0����ʾ�x������

�� WS��1����ʾ�x������

WSҲ�Q���r�����LRCLK/Left RightClock��WS�l�ʵ������IJɘ��ʡ�WS�ȿ�����SCK�������أ�Ҳ������SCK���½���׃�������O����SCK�������زɘ�WS��̖��������̖MSB��WS��׃��ĵڶ����r犣�SCK����������Ч�������tһ��SCK�����@�ӿ������O�������ĕr�g�Դ惦��ǰ���յĔ��������ʂ�ý�����һ�M������

|